kategoriler: Pratik Elektronik, Acemi elektrikçiler

Görüntülenme sayısı: 74031

Makaleye Yorumlar: 0

Mantık yongaları. Bölüm 9. JK tetikleyicisi

JK tetikleyici hakkında bir hikaye ve çalışmalarını incelemek için basit deneyler.

JK tetikleyici hakkında bir hikaye ve çalışmalarını incelemek için basit deneyler.

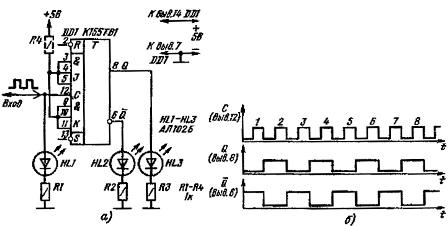

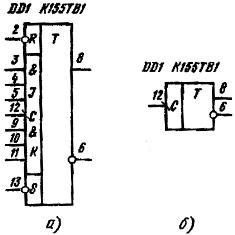

Makalenin önceki bölümlerinde RS ve D gibi tetikleyiciler açıklanmıştı, eğer bahsetmezseniz bu hikaye tamamlanmayacak Jk tetikleyici. Yanı sıra D tetikleyici Gelişmiş giriş mantığı vardır. 155 serisinde bu, DIP-14 paketinde üretilen bir K155TV1 yongasıdır. Pinout'u veya şimdi söyledikleri gibi, pinout (İngilizce PIN - pininden) Şekil 1a'da gösterilmiştir. Yabancı analogları SN7472N, SN7472J.

Belirli bir şemada herhangi bir sonuç kullanılmazsa, Şekil 1b'de gösterildiği gibi basitçe gösterilmemesi tamamen kabul edilebilir.

Sonuçların tanımı ve amacı

K155TV1 tetikleyici doğrudan ve ters çıkışlara sahiptir. Şekilde bunlar sırasıyla 8 ve 6 sonuçlarıdır.Amaçları daha önce dikkate alınan D ve RS tipi tetikleyicilerle aynıdır. Ters çıkış küçük bir daire içinde başlar.

R ve S girişlerinde, tetikleyici basit bir gibi çalışır RS tetikleyici. Bu girişlerin çalışma seviyesi düşüktür, bu terminallerin tabanındaki dairelerle gösterilir. D - tetiklemede olduğu gibi, bu girişler önceliklidir: bunlardan birinde düşük bir seviyenin görünümü ve tutulması, girişlerin geri kalanını yasaklar ve kısa bir negatif darbe, C girişindeki bir sonraki darbeye kadar tetiği ilgili duruma aktarır.

C girişi saatlidir. Tetik sayma modunda çalıştığında, bilginin rolünü oynar - sayım darbelerinin gelmesi tam olarak üzerindedir. Bilgi alma ve depolama modunda, bir saat olarak hizmet eder, amacı bir D-tetikleyicisinin benzer bir girişine benzer, ancak çalışma mantığı biraz farklıdır ve JK girişlerinin durumuna göre belirlenir.

Şekil 1. K155TV1 yongasının pin çıkışı.

J ve K tetik kontrol girişleridir. Grafik sembolünde & - mantıksal I sembolü ile gösterilen şema 3I'ya göre birleştirilir.Çoğu zaman, bu girişler devrelerde birbirine bağlanır, bir J ve bir K girişine sahip olduğu ortaya çıkar. Bazı mikro devreler serisinde JK tetikleyicileri de vardır, bunlara TB1 de denir, ancak 155 serisinin aksine bir J ve K girişi vardır. Bu girişler üzerindeki çalışma mantığı K155TV1 ile tamamen aynıdır, ancak 3 üst düzey mantık sinyalini bir araya getirmeniz gerekmez. Bu mikro devrelere bir örnek, örneğin K176TV1, K561TV1, K1564TV1'e hizmet edebilir.

JK tetikleyicisinin mantığını öğrenme

JK tetiğinin çalışması hakkında daha fazla bilgi edinmek için, önceki makalede olduğu gibi breadboard'da açmanız ve giriş sinyallerini manuel olarak göndermeniz yeterlidir. Gerçekten de, gitar veya düğme akordeonunu çalma konusunda bir kendi kendine kullanım kılavuzunu ezberleyebileceğinizi itiraf etmelisiniz, ancak enstrümanı almadan, çalmayı öğrenemezsiniz. Ayrıca mikro devreler durumunda: en basit deneyleri yapana kadar, çalışmanın anlamını anlamak zor olacaktır.

Giriş sinyalleri olarak, D tetikleyicisini incelerken, ortak bir kabloya bağlı bir tel atlama kablosu kullanacağız.

JK tetiği K155TV1'i test etmek için devre Şekil 2'de gösterilmiştir.

Şekil 2. JK tetiği K155TV1'i test edin.

Besleme voltajı, şemada oklarla iletken şeklinde gösterilen mikro devrenin 14. ve 7. sonuçlarına her zamanki gibi beslenir.

Tetikleyicinin durumunun görsel olarak izlenmesi için LED göstergeleri çıkışlarına doğrudan ve ters bağlanır. Aynı gösterge C girişine bağlanır. LED ışıması, bu çıkışta mantıksal bir birim seviyesinin (2.4 ... 5V) olduğunu gösterir. C girişinde, C girişine bağlı puls üretecinin çıkış sinyalinin seviyesi görüntülenecektir Tabii ki, böyle düşük bir frekanstaki giriş ve çıkışların durumu, sıradan bir voltmetre kullanarak gözlemlemek oldukça mümkündür, ancak bu çok uygun değildir.

RS üzerinde JK tetikleme işlemi - girişler

Devre açılmadan önce çok basit olmasına rağmen, her zamanki gibi, hataları, kısa devreleri ve kopmaları kontrol etmelisiniz: sadece ters yönde gücü açmak bile mikro devreyi kullanılamaz hale getirebilir. Bu kural, sadece yarı iletken aygıtları olmayan bir elektrik devresi olsa bile, tüm bu durumlarda hatırlanmalı ve uygulanmalıdır.

Öyleyse aç. İlk açtığınızda, çıkıştaki LED'lerden biri yanmalıdır, bu bilinmiyor. Bu, açıldığında geçici durumlardan kaynaklanır. Şimdi, yukarıda bahsedilen tel atlama telini kullanarak, alternatif olarak R ve S girişlerine düşük bir mantık seviyesi uygulayacağız. Bu durumda, çıkıştaki LED'ler, tetikleyicinin durumunu gösteren dönüşümlü olarak değişmelidir. Bu çalışma moduna eşzamansız denir - ek flaş (devrede, saat) sinyalleri gerektirmez.

Doğrudan R ve S girişlerine aynı anda düşük bir seviye uygulamak gerekli değildir: bu durum tetikleyici için yasak olarak kabul edilir. Mikro devrenin bir çıkışı şeklinde geri dönüşü olmayan sonuçlara yol açmayacak olsa da, bu durumda çıkışların durumu bilinmeyecektir, bu da tetikleyicinin mantığına karşılık gelmez. Her şey yolundaysa, JK girişlerinde bir tetikleyicinin çalışmasını incelemek için deneylere gidebilirsiniz.

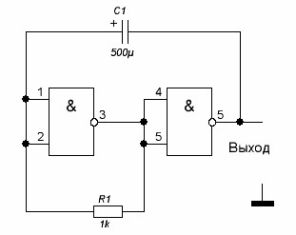

JK girişlerine bir atlama teli ile düşük bir kablo uygulanırsa ne olur? Hiçbir şey: tetik, göstergelerin parıltısı ile görülebilecek önceki durumu depolayacaktır. Bu girişlerin tetikleyicinin durumunu etkilemesi için, devresi Şekil 3'te gösterilen jeneratörden C girişine darbeler uygulamak gerekir. Bunu monte etmek için ek bir K155LA3 yongası gereklidir. Nabız tekrarlama hızı ve süresi, tetikleyici durumların görsel olarak izlenebileceği şekilde olmalıdır.

Şekil 3. Saat üreteci.

Sayma modunda JK tetikleme işlemi

JK girişleri Şekil 2a'da gösterildiği gibi bağlanırsa, tetikleme sayma modunda çalışır: her giriş darbesinde tetikleyicinin durumu değişir. Direnç R4, şemada noktalı bir çizgi ile gösterilmiştir - koyamazsınız, çünkü bağlı olmayan girişler hala mantıksal bir ünite durumundadır. Bu direncin temel amacı JK girişleri yoluyla parazite karşı koruma sağlamaktır.

JK tetikleyicisinin zamanlama diyagramı Şekil 2b'de gösterilmiştir ve D tetikleyici için benzer bir şemaya çok benzer. Temel fark, tetikleme durumunun C girişindeki pozitif seviye farkı nedeniyle değil, negatif olanı - giriş darbesinin seviyesi yüksek seviyeden düşük seviyeye değiştiğinde değişmesidir.

Tetikleyicinin çıkışındaki darbelerin frekansının, giriş darbelerinin frekansından tam olarak iki kat daha düşük olduğunu görmek kolaydır. Bu nedenle, sayma modundaki tetikleyiciler genellikle iki tarafından frekans bölücüler olarak kullanılır. Serilere dahil edilen iki tetikleyici frekansı dörde böler ve üç tetikleyici zaten sekize bölünür ve böylece 2'nin gücüne göre devam eder.

Tek bir katsayı katsayısına sahip bir frekans bölücü gerekiyorsa, geri bildirimli birkaç tetikleyici kullanılır, ancak bu, sayacın ve darbe şekillendiricileri hakkındaki makalenin bir sonraki bölümünde tartışılacaktır.

Yukarıdakilerden sonuca varabiliriz: JK girişleri aynı anda bir mantıksal birim durumundaysa (yüksek seviye), tetik sayma modunda çalışır. Bu, C girişindeki her negatif seviye farkı için tetikleme durumunun tersine değiştiği anlamına gelir.

JK girişlerinde tetikleme işlemi

JK girişlerinde mantıksal sıfır seviyesi varsa ne olur? Bunu kontrol etmek için, en az bir JK girişini (K155TV1'in 3I devresine göre birleştirilmiş 3 J ve 3 K girişine sahip olduğunu hatırlayın) ortak bir kabloya bağlamak yeterlidir. Ancak ortak kabloya ve JK'nın tüm girişlerine bağlanabilirsiniz, bu zaten ilkesizdir. LED göstergelerine göre, saat darbelerinin geldiğini ve tetikleme durumunun değişmediğini görüyoruz.J ve K girişlerinde mantığın sıfır olduğu bir durumda, JK - tetikleyici bilgi depolama modundadır.

İki vakayı ele almaya devam ediyor. Birinci durum J girişi yüksek ve K girişi düşüktür. Bu durumda, C girişindeki tetikleyici tek bir duruma ayarlanır - tetikleyicinin doğrudan çıkışına bağlı HL3 göstergesi yanar. HL2, elbette, geri ödenir.

JK girişlerinin durumu gelecekte değişmezse, C girişindeki her puls, tetikleyiciyi zaten olmasına rağmen tek bir duruma ayarlamaya eğilimlidir. Bu durumda, C girişinde, bu durumda önceki tetikleme durumunun basitçe doğrulandığını söylerler.

İkinci durum, J girişinin sıfır ve K girişinin bir olduğu durumdur. Bu durumda, JK girişlerinde, C girişindeki ilk darbe, tetik sıfır olarak ayarlanır (sıfırlanır) - HL3 göstergesi kapanır ve HL2 açılır. JK girişlerinin durumu değişmezse, C girişi de yukarıda açıklandığı gibi sadece bu kez sıfır durumunu teyit eder.

Yani, hatırlamayı kolaylaştırmak, özetlemek gerekirse: JK girişlerindeki iki birim sayma modudur. Koşul 3I'nin JK girişleri için yerine getirildiği anlaşılmaktadır: biri J girişinin üçünde ve biri K girişinin üçünde.

JK girişlerinde iki sıfır - bilgi depolama modu: tetikleyici durumunun C girişindeki darbeler değiştirilemez. Böyle bir durumu elde etmek için, en az bir J girişinin olması ve en az bir K girişinin mantık sıfır seviyesine sahip olması yeterlidir.

Her üç J girişinin de yüksek olması durumunda, tetikleyici tek bir duruma ayarlanır. Aynı zamanda, K'nin 3 girişinden en az birinin seviyesi düşük olmalıdır.

Bir tetikleyiciyi sıfırlamak için, J girişlerinden en az birinde sıfır, K girişinin üçünde de bir tane tutulmalıdır.

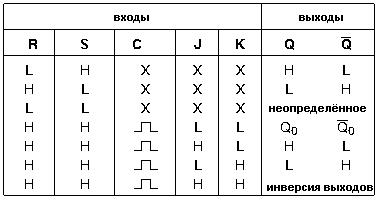

Yukarıda yazılı olan her şey, Şekil 4'te gösterilen K155TV1 tetikleyicisinin doğruluk tablosunda bulunabilir.

Şekil 4. K155TV1 yongası için doğruluk tablosu.

Çeşitli tipteki tetikleyiciler, sayma cihazlarının elemanları olarak veya sadece sayaçların yanı sıra darbe şekillendiricileri olarak da kullanılır. Bu, mantık devreleri hakkındaki makalenin bir sonraki bölümünde tartışılacaktır.

Makalenin devamı: Mantık yongaları. Bölüm 10. Kişilerin sıçramadan nasıl kurtulurum

Ayrıca bkz. electro-tr.tomathouse.com

: