kategoriler: Öne Çıkan Makaleler » Pratik Elektronik

Görüntülenme sayısı: 8430

Makaleye Yorumlar: 0

Schmitt tetikleyici - genel görünüm

Darbe devresinin tasarımı sırasında geliştiricinin, dikdörtgen olmayan bir şeklin (örneğin testere dişi veya sinüzoidal) giriş sinyalinden belirli yüksek ve düşük voltaj seviyelerine sahip saf bir dikdörtgen sinyal oluşturabilen bir eşik cihazına ihtiyacı olabilir.

Schmitt tetikleyici, giriş sinyalinin etkisi altında, bir sıçrama halinde birbirini değiştiren, iyi oturan, yani çıktı dikdörtgen bir sinyaldir.

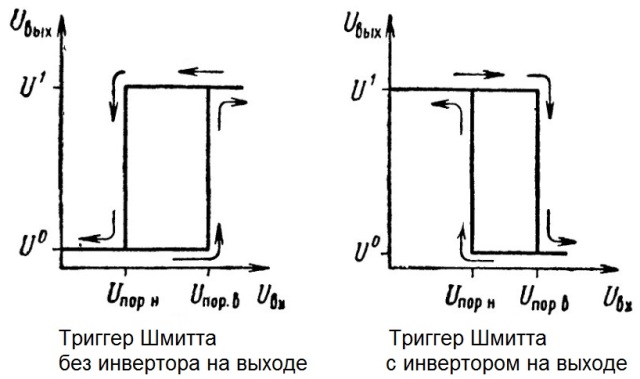

Schmitt tetikleyicinin karakteristik bir özelliği, giriş sinyalinin çıkış voltajı bu tetikleyicinin çıkışında düşük bir seviyeden yüksek bir seviyeye çevrildiğinde ve bunun tersi olduğunda, giriş sinyali için voltaj seviyeleri arasında belirli bir aralığın varlığıdır.

Schmitt tetikleyicisinin bu özelliğine histerezis denir ve karakteristiğin eşik giriş değerleri arasındaki kısmına histerezis bölgesi denir. Schmitt tetikleyici girişi için üst ve alt eşik değerleri arasındaki fark, tetikleyicinin hassasiyetinin bir ölçüsü olan histerezis bölgesinin genişliğini belirler. Histerezis bölgesi ne kadar genişse - Schmitt tetikleyicisi o kadar az duyarlıdır, histerezis bölgesi daralır - hassasiyeti o kadar yüksek olur.

Schmitt tetikleyicileri, aynı anda bir gövdenin içine birkaç ayrı tetikleyicinin yerleştirilebildiği özel mikro devreler biçiminde mevcuttur. Bu tür mikro devreler belirli bir normalize edilmiş anahtarlama eşiğine sahiptir ve dikdörtgen bir şekilden uzak olan giriş sinyaline rağmen çıkışta dik cepheler verir. Ek olarak, Schmitt tetikleyici de mantıksal elemanlar temelinde inşa edilebilir, bu durumda geliştirici eşik cihazının histerezis bölgesinin genişliğini çok doğru bir şekilde ayarlama ve ayarlama fırsatına sahiptir.

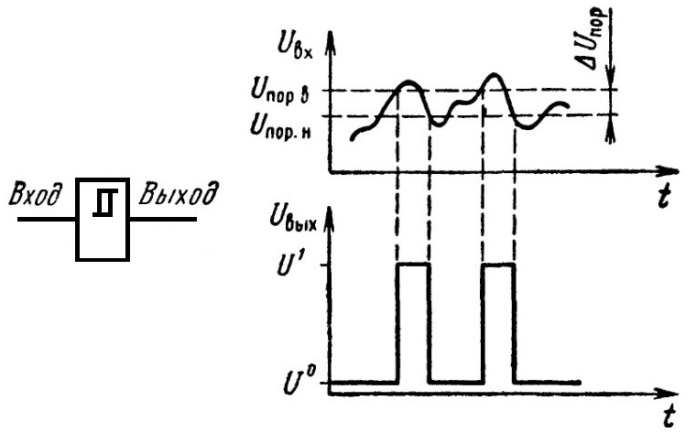

Şekle dikkat edin ve Schmitt tetikleyicisinin prensibini daha yakından inceleyin.

Burada bir tetikleyici elemanın şematik bir resminin yanı sıra aktarım ve zaman özellikleri gösterilmektedir. Gördüğünüz gibi, giriş sinyali seviyesi Uin, alt Ufor eşiğinden daha düşük olduğunda, Schmitt tetikleyici çıkışı da buna göre sıfıra yakın bir düşük voltaj seviyesine U0 sahiptir.

Giriş sinyalinin Uin voltajını artırma sürecinde, değeri önce histerezis bölgesi Uпор.н'in alt sınırına ulaşır, daha düşük eşik, çıkış daha önce olduğu gibi hiçbir şeyi değiştirmez. Ve giriş voltajı Uin histerezis bölgesine girdiğinde ve bir süre içindeyken bile, çıkışta hiçbir şey olmaz - çıkış hala düşük seviye voltajı U0'dır.

Ancak giriş voltajı Uin seviyesi, histerezis bölgesi Ufor.in (yanıt alanı) üst eşiği ile karşılaştırılır karşılaştırılmaz, tetik çıkışı yüksek bir voltaj seviyesi U1 durumuna atlar. Giriş voltajı Uin daha da artmaya devam ederse (mikro devre için izin verilen sınırlar dahilinde), iki kararlı durumdan birine ulaşıldığı için çıkış voltajı Uout artık değişmeyecektir - yüksek bir U1 seviyesi.

Şimdi, diyelim ki Uin giriş voltajı düşmeye başladı. Histerezis bölgesine dönerken, çıktıda değişiklik olmaz; seviye hala yüksek U1'dir. Ancak giriş sinyalinin Uin voltajı, histerezis bölgesi Uпн.н'in alt sınırına eşit olur olmaz - Schmitt tetikleme çıkışı, düşük voltaj seviyesi U0 olan duruma atlar. Schmitt tetikleyicisinin çalışması buna dayanmaktadır.

Bazen Schmitt tetikleyicilerinin faydalı olduğu kanıtlanır, burada “I” mantık elemanı mikro devrenin içine uygulanır ve çıkışta “NOT” invertörü kurulur (Schmitt ters çevirme tetiği).Bu durumda, aktarım karakteristiği diğer yöne bakacaktır: voltaj, histerezis bölgesinin üst sınırının ötesine geçtiğinde, Schmitt tetiğinin çıkışında düşük bir seviye görünür ve histerezis bölgesinin altına döndüğünde, çıkışta yüksek bir seviye görünür. Bu pratik olarak histerezisli bir AND-NOT elemanıdır.

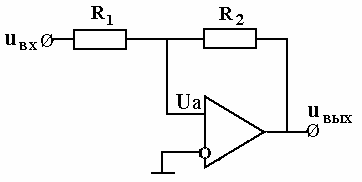

Schmitt tetikleyici monte edilebilir ve işlemsel bir amplifikatörde (op amp). Genel anlamda uygulanması için seçeneklerden birine bakalım. Op-amp'in evirici girişi topraklanır ve giriş sinyali, R1 direnci üzerinden op-amp'in evirici olmayan girişine beslenir. Op-amp'in direnç R2 boyunca geri besleme zinciri boyunca çıkışı, op-amp'in evirmeyen girişine bağlanır. Dikdörtgen voltaj, op amp çıkışından çıkarılır.

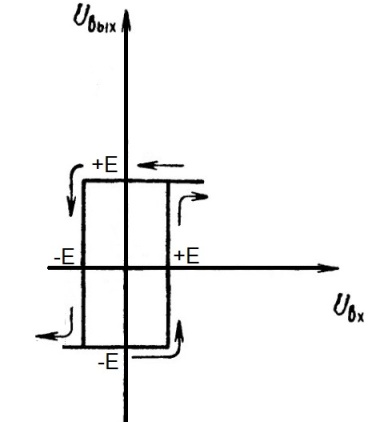

İşlemsel amplifikatörün çıkışındaki voltaj geleneksel olarak Uout = K * Ua formülü ile belirlenir. Genellikle Uout.max op-amp besleme voltajına eşittir (kayın E ile gösterelim) ve K opamp kazancıdır, 1.000.000 civarındadır.Çıkış voltajı + E ila -E arasında değişebilir. Burada belirli ayrıntılara girmeyeceğiz ve anlayışı basitleştirmek için, geri besleme devresindeki giriş direnci ve direncin birbirine eşit olduğu canlı bir örneği ele alacağız: R1 = R2.

Bu nedenle, en başında, Uin = 0 ve dolayısıyla Ua = 0 olduğunda, Uout = 0, çünkü op-amp'in ters çevirmeyen girişindeki voltaj, ters girişindeki voltajı aşmaz.

Şimdi Uvh biraz artarsa, Ua da biraz artacaktır. Daha sonra Uout, (K değerine göre) önemli ölçüde artacaktır, çünkü op-amp'in ters çevirmeyen girişindeki voltaj, karar verdiğimiz gibi topraklanan ters girişindeki voltajı aşacaktır. Daha sonra, Ua noktasının yukarıdaki şemaya göre bağlanan dirençler arasında olması nedeniyle, Ua noktasında voltaj önemli ölçüde artacak, yaklaşık Uout / 2 olacak ve olumlu geri bildirim çığından dolayı, kararlı bir voltaj Uout (besleme voltajına eşit) OS = E). Böylece, op-amp, yüksek çıkış voltaj seviyesine sahip kararlı bir duruma geçti. Ayrıca, Ua = (E + Uin) / 2.

Bu durumda Uin'i azaltmaya başlarsak, o zaman sıfıra eşit olsa bile, o zaman Ua noktasında hala E / 2 olacaktır ve op-amp'in çıkışında hala yüksek bir voltaj Uout = E olacaktır.

Sadece Uin -E'ye eşit olduğunda, ancak o zaman Ua sıfıra eşit olur ve op-amp çıkışı düşük voltaj seviyesine (-E) bir duruma geçer. Bu durumda, bir geri bildirim çığ tekrar ortaya çıkacaktır - şimdi Uout = -E, Ua = (Uin-E) / 2 ve bu, op-amp'in evirmeyen girişinden çok daha düşük. Tetik, düşük çıkış seviyesine sahip sabit bir duruma girdi. Op amp çıkışının şimdi yüksek bir duruma dönmesi için, Uin'in tekrar E'ye eşit olması ve başka bir geri bildirim çığına neden olması gerekir. Sıfır noktasına dönüş artık gerçekleşmeyecek.

Ayrıca bkz. electro-tr.tomathouse.com

: