kategoriler: Öne Çıkan Makaleler » Pratik Elektronik

Görüntülenme sayısı: 113767

Makaleye yorum: 5

Entegre zamanlayıcı NE555 - tarih, tasarım ve kullanım

Çok popüler bir çipin yaratılış tarihi ve iç yapısının açıklaması

Elektronik efsanelerinden biri entegre devre yongası NE555. 1972 yılında geliştirildi. Bu uzun ömür, her yongadan uzaktır ve her transistörden bile değildir. Peki, işaretlemesinde üç beş tane olan bu mikro devre hakkında özel olan nedir?

Elektronik efsanelerinden biri entegre devre yongası NE555. 1972 yılında geliştirildi. Bu uzun ömür, her yongadan uzaktır ve her transistörden bile değildir. Peki, işaretlemesinde üç beş tane olan bu mikro devre hakkında özel olan nedir?

Signetics, NE555 Chip'in Seri Üretimini Başlattı tam bir yıl sonra Hans R. Kamensind tarafından geliştirilmiştir.. Bu hikayedeki en şaşırtıcı şey, o zamanlar Kamensind'in işsiz olduğuydı: PR Mallory'den ayrıldı, ancak hiçbir yere ulaşmayı başaramadı. Aslında bu bir “ödev” idi.

Çip, günün ışığını gördü ve elbette Kamensind'in bir arkadaşı olan Signetics yöneticisi Art Fury'nin çabaları sayesinde büyük bir ün ve popülerlik kazandı. General Electric için çalışıyordu, bu yüzden orada neye ihtiyaç duyulduğunu ve potansiyel bir alıcının dikkatini nasıl çekeceğini elektronik pazarını biliyordu.

Kamensinda A.Fury'nin anılarına göre, zanaatının gerçek bir meraklısı ve sevgilisiydi. Evde, radyo bileşenleri ile dolu bir laboratuvar vardı, burada çeşitli çalışmalar ve deneyler yaptı. Bu, geniş pratik deneyim biriktirmeyi ve teorik bilgiyi derinleştirmeyi mümkün kıldı.

O zaman, Signetics ürünleri “5 **” olarak adlandırıldı ve elektronik pazarında doğaüstü bir anlayışa sahip olan deneyimli A. Fury, 555 (üç beşlik) işaretinin yeni çip için en hoş olacağına karar verdi. Ve yanılmıyordu: mikro devre sadece sıcak kekler gibi gitti, belki de mikro devrelerin yaratıldığı tarih boyunca en büyük haline geldi. En ilginç şey, mikro devrenin günümüze olan ilgisini kaybetmemiş olmasıdır.

Bir süre sonra, mikro devrenin işaretlemesinde iki harf belirdi, NE555 olarak biliniyordu. Ancak o günlerde patent sisteminde tam bir karışıklık olduğu için, entegre zamanlayıcı, tembel olmayan herkesi serbest bırakmak için koştu, doğal olarak, üç betanın önüne üç harf (seninkini oku) koydu. Daha sonra, 555 zamanlayıcıya dayanarak, elbette, daha çok pimli durumlarda çift (IN556N) ve dörtlü (IN558N) zamanlayıcılar geliştirildi. Ancak temel hala NE555'teydi.

Şek. 1. Entegre zamanlayıcı NE555

SSCB'de 555

Yerli radyo-teknik literatürdeki 555'in ilk tanımı 1975'te Electronics dergisinde yayınlandı. Makalenin yazarları, bu çipin o zamanlar yaygın olarak bilinen operasyonel amplifikatörlerden daha az popülerliğe sahip olmayacağını belirtti. Ve onlar hiç yanılmıyordu. Mikro devre çok basit tasarımlar yaratmayı mümkün kıldı ve neredeyse hepsi acı verici bir ayarlama yapmadan hemen çalışmaya başladı. Ancak, tasarımın evde tekrarlanabilirliğinin, "basitliğinin" karesi ile orantılı olarak arttığı bilinmektedir.

80'lerin sonlarında Sovyetler Birliği'nde, 555 adında tam bir analog geliştirildi. KR1006VI1. Yerli analoğun ilk endüstriyel uygulaması Vm12 Electronics video kaydedicisindeydi.

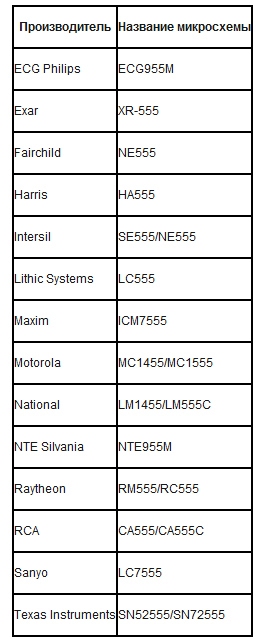

Chip üreticileri NE555:

Dahili cihaz yongası NE555

Havya tutmadan ve yapının integral zamanlayıcıda montajına başlamadan önce, içinde ne olduğunu ve nasıl çalıştığını anlayalım. Bundan sonra, belirli bir pratik şemanın nasıl çalıştığını anlamak çok daha kolay olacaktır.

Entegre zamanlayıcı yirminin üzerinde transistörlerbağlantısı şekilde gösterilen - https://electro-tr.tomathouse.com/555ic.jpg

Gördüğünüz gibi, devre şeması oldukça karmaşıktır ve burada sadece genel bilgi için verilmiştir.Sonuçta, yine de bir havya ile içine giremezsiniz, tamir edemezsiniz. Aslında, hem dijital hem de analog diğer tüm mikro devrelerin içeriden baktığı şey tam olarak budur (bkz. Efsanevi Analog Cipsler). Entegre devrelerin üretimi için kullanılan teknoloji budur. Cihazın mantığını böyle bir şema ile bir bütün olarak anlamak da mümkün olmayacaktır, bu nedenle fonksiyonel şema aşağıda gösterilmiştir ve açıklaması verilmiştir.

Teknik veriler

Ancak, çip mantığı ile uğraşmadan önce, muhtemelen elektrik parametrelerini getirmelisiniz. Besleme voltajı aralığı yeterince geniş 4.5 ... 18V'dir ve çıkış akımı 200mA'ya ulaşabilir, bu da düşük güç rölelerinin yük olarak bile kullanılmasına izin verir. Çipin kendisi çok az tüketir: yük akımına sadece 3 ... 6 mA eklenir. Aynı zamanda, zamanlayıcının kendisinin doğruluğu pratikte besleme voltajından bağımsızdır - hesaplanan değerin sadece yüzde 1'i. Sapma sadece% 0.1 / volttur. Sıcaklık sapması da küçüktür - sadece 0,% 005 / ° C. Gördüğünüz gibi, her şey oldukça kararlı.

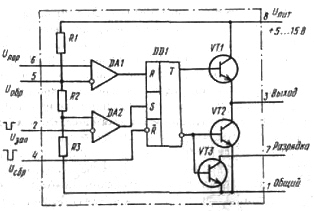

NE555'in fonksiyonel diyagramı (KR1006VI1)

Yukarıda belirtildiği gibi, SSCB'de burjuva NE555'in bir analogu yaptılar ve buna KR1006VI1 adını verdiler. Analog, orijinalinden daha kötü değil, çok başarılı olduğu ortaya çıktı, böylece herhangi bir korku veya şüphe olmadan kullanabilirsiniz. Şekil 3, entegre zamanlayıcı KR1006VI1'in fonksiyonel diyagramını göstermektedir. NE555 yongası ile tamamen tutarlıdır.

Şekil 3. KR1006VI1 entegre zamanlayıcısının fonksiyonel diyagramı

Çipin kendisi çok büyük değil - sekiz pimli bir DIP8 paketinde ve küçük boyutlu bir SOIC8'de mevcut. İkincisi, 555'in SMD düzenleme için kullanılabileceğini, başka bir deyişle geliştiricilerin hala ilgi duyduğunu öne sürüyor.

Mikro devrenin içinde de birkaç element vardır. Ana olan en yaygın RS bir tetikleyicidir DD1. Bir mantıksal birim R girişine beslendiğinde, tetikleyici sıfıra sıfırlanır ve bir mantıksal birim S girişine beslendiğinde, doğal olarak bire ayarlanır. RS girişlerinde kontrol sinyalleri üretmek için karşılaştırıcılar üzerinde özel devrebiraz sonra tartışılacak.

Mantıksal bir birimin fiziksel seviyeleri, elbette, kullanılan besleme voltajına bağlıdır ve pratik olarak Upit / 2'den neredeyse tam Upit'e kadar değişir. CMOS yapısının mantık mikro devreleri için yaklaşık olarak aynı oran gözlenir. Mantıksal sıfır, her zamanki gibi 0 ... 0.4V'dir. Ancak bu seviyeler mikro devrenin içinde, sadece onları tahmin edebilirsiniz, ancak onları ellerinizle hissedemezsiniz, gözlerinizle göremezsiniz.

Çıktı aşaması

VT1, VT2 transistörleri üzerinde güçlü bir çıkış aşaması olan çipin yük kapasitesini arttırmak için, tetikleyicinin çıkışına bağlanır.

RS tetiği sıfırlanırsa, çıkış (pin 3) bir mantık sıfır voltajı içerir, yani. açık transistör VT2. Tetikleyicinin çıkışa monte edilmesi durumunda, mantıksal birimin seviyesi de olur.

Çıkış katı, yükü çıkış ve ortak kablo (terminaller 3.1) veya güç barası (terminaller 3.8) arasında bağlamanızı sağlayan bir itme-çekme devresi tarafından yapılır.

Çıkış aşamasında küçük bir açıklama. Dijital mikro devrelerdeki cihazları tamir ederken ve ayarlarken, devreyi kontrol etmenin yöntemlerinden biri mikro devrelerin giriş ve çıkışlarına düşük seviyeli bir sinyal vermektir. Kural olarak, bu, mikro devreye herhangi bir zarar vermemekle birlikte, bir dikiş iğnesi yardımıyla bu giriş ve çıkışların ortak teline kısa devre yapılarak yapılır.

Bazı devrelerde, NE555 güç kaynağı 5V'dir, bu yüzden bu aynı zamanda dijital mantıktır ve bunu da oldukça özgürce yapabilirsiniz. Ama gerçekte bu böyle değil. 555 yongası veya daha ziyade itme-çekme çıkışı ile bu tür "deneyler" yapılamaz: çıkış transistörü VT1 şu anda açıksa, kısa bir devre açılır ve transistör basitçe yanar. Besleme gerilimi maksimuma yakınsa, acınacak bir sonlanma kaçınılmazdır.

Ek transistör (pim 7)

Bahsedilen transistörlere ek olarak, bir transistör VT3 de vardır. Bu transistörün toplayıcısı çip 7 "Deşarj" çıkışına bağlanır. Amacı, mikro devreyi puls üreteci olarak kullanırken zaman ayar kondansatörünü boşaltmaktır. DD1 tetiği sıfırlandığında kapasitörün deşarjı gerçekleşir. Tetiğin açıklamasını hatırlarsak, o zaman ters çıkışta (şemada bir daire ile gösterilir), VT3'ün transistörünün açılmasına yol açan mantıksal bir birim vardır.

Sıfırlama sinyali hakkında (pin 4)

Bir tetikleyiciyi istediğiniz zaman sıfırlayabilirsiniz - “sıfırlama” sinyali yüksek önceliğe sahiptir. Bunu yapmak için, şekilde Usbr olarak gösterilen özel bir R girişi (pin 4) vardır. Şekilden de anlaşılacağı gibi, 4. çıkışa 0.7V'dan daha düşük olmayan düşük seviyeli bir darbe uygulanırsa bir sıfırlama meydana gelir. Aynı zamanda, mikro devrenin çıkışında düşük bir voltaj görünecektir (pim 3).

Bu girişin kullanılmadığı durumlarda, dürtü gürültüsünden kurtulmak için bir mantıksal birim seviyesi uygulanır. Bunu yapmanın en kolay yolu, pimi 4 doğrudan güç barasına bağlamaktır. Hiçbir durumda, dedikleri gibi, "havada" bırakmamalısınız. O zaman merak etmeli ve uzun süre düşünmelisiniz ve devre neden bu kadar dengesiz çalışıyor?

Genel tetikleyici notları

Tetiğin durumu hakkında tamamen karıştırılmamak için, tetikleyici hakkındaki tartışmalarda doğrudan çıkış durumunun her zaman dikkate alındığı hatırlanmalıdır. Tetikleyicinin “kurulu” olduğu söylenirse, doğrudan çıkışta mantıksal birimin durumu. Tetikleyicinin "sıfırlandığını" söylerse, doğrudan çıkışın kesinlikle mantıksal sıfır durumuna sahip olacağı kesin.

Ters çıkışta (küçük bir daire ile işaretlenmiş) her şey tam tersi olacaktır, bu nedenle genellikle tetikleme çıkışına parafaz denir. Her şeyi tekrar karıştırmamak için artık bunun hakkında konuşmayacağız.

Bu yere dikkatlice okuyan herkes şu soruyu sorabilir: “Affedersiniz, çıkışta güçlü bir transistör kaskadına sahip bir tetikleyicidir. Zamanlayıcının kendisi nerede? ” Ve haklı olacak, çünkü konu henüz zamanlayıcıya ulaşmadı. Bir zamanlayıcı almak için Hans R. Kamensind'in yaratıcısı babası bu tetikleyiciyi kontrol etmek için orijinal bir yol icat etti. Bu yöntemin püf noktası kontrol sinyallerinin oluşmasıdır.

RS üzerinde sinyal üretimi - tetikleyicinin girişleri

Ne elde ettik? DD1 tetiği zamanlayıcıdaki her şeyi kontrol eder: eğer birine ayarlanırsa, çıkış voltajı yüksektir ve sıfırlanırsa, çıkış 3 düşüktür ve buna ek olarak VT3 transistörü açıktır. Bu transistörün amacı bir devrede bir zamanlama kondansatörünü, örneğin bir puls üretecini boşaltmaktır.

DD1 tetiği DA1 ve DA2 karşılaştırıcıları kullanılarak kontrol edilir. Tetiğin karşılaştırıcıların çıkışlarındaki çalışmasını kontrol etmek için, yüksek seviye sinyalleri R ve S'nin elde edilmesi gerekir. R1 ... R3 dirençlerinde hassas bir bölücü tarafından üretilen her karşılaştırıcının girişlerinden birine bir referans gerilimi uygulanır. Dirençlerin direnci aynıdır, bu nedenle onlara uygulanan voltaj 3 eşit parçaya bölünür.

Tetik kontrol sinyali üretimi

Zamanlayıcı başlatma

1 / 3U'luk doğrudan voltaj karşılaştırıcı DA2'nin doğrudan girişine uygulanır ve zamanlayıcı Uzap'ı pim 2 üzerinden başlatmak için harici voltaj, karşılaştırıcının ters girişine uygulanır. Bu karşılaştırıcının çıkışında DD1 tetikleyicisinin S girişine etki etmek için yüksek bir seviye elde etmek gerekir. Ustap voltajı 0 ... 1 / 3U aralığındaysa bu mümkündür.

Böyle bir voltajın kısa süreli bir darbesi bile DD1 tetikleyicisini ve yüksek seviyeli bir voltaj zamanlayıcısının görünümünü tetikleyecektir. Ucap girişi 1 / 3U üzerindeki ve besleme voltajına kadar olan voltajlara maruz kalırsa, mikro devrenin çıkışında herhangi bir değişiklik olmaz.

Zamanlayıcı durdurma

Zamanlayıcıyı durdurmak için, sadece DD1 dahili tetikleyicisini sıfırlamanız gerekir ve bunun için DA1 karşılaştırıcısının çıkışında yüksek seviyeli bir R sinyali oluşturun. DA1 karşılaştırıcısı DA2'den biraz farklı açılır.2 / 3U referans gerilimi evirici girişine uygulanır ve "Giriş eşiği" kontrol sinyali doğrudan girişe uygulanır.

Bu dahil etme ile, DA1 karşılaştırıcısının çıkışında yüksek bir seviye, sadece doğrudan girişteki Upoor gerilimi, ters çevirici üzerindeki referans gerilimi 2 / 3U'yu aştığında ortaya çıkar. Bu durumda, DD1 tetiği sıfırlanacak ve mikro devrenin çıkışında düşük bir seviye sinyali oluşturulacaktır (pin 3). Ayrıca, zaman ayar kondansatörünü deşarj edecek “deşarj” VT3 transistörü açılır.

Giriş voltajı 1 / 3U ... 2 / 3U içindeyse, karşılaştırıcılardan biri çalışmaz, zamanlayıcının çıkışında durum değişikliği olmaz. Dijital teknolojide bu voltaja “gri seviye” denir. Sadece 2 ve 6 pinlerini bağlarsanız, 1 / 3U ve 2 / 3U yanıt seviyelerine sahip bir karşılaştırıcı alırsınız. Ve tek bir ek ayrıntı olmadan bile!

Referans voltaj değişimi

Şekilde Uobr olarak gösterilen Sonuç 5, ek dirençler kullanarak referans voltajını veya değişikliklerini kontrol etmek için tasarlanmıştır. Bu girişe bir kontrol voltajı sağlamak da mümkündür, böylece bir frekans veya faz modülasyonlu sinyal elde etmek mümkündür. Ancak daha sıklıkla bu sonuç kullanılmaz ve girişimin etkisini azaltmak için küçük kapasiteli bir kapasitör aracılığıyla ortak bir kabloya bağlanır.

Mikro devre 1 - GND, 2 + U pimleri üzerinden beslenir.

İşte NE555 entegre zamanlayıcının gerçek açıklaması. Zamanlayıcı, aşağıdaki makalelerde tartışılacak olan her türlü şemayı topladı.

Boris Aladyshkin

Makalenin devamı: 555 Tümleşik Zamanlayıcı Tasarımları

Ayrıca bkz. electro-tr.tomathouse.com

: